| Главная » Статьи » Компьютеры » Познавательные статьи |

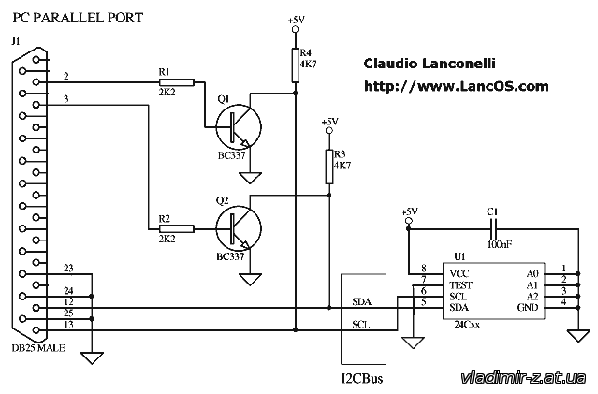

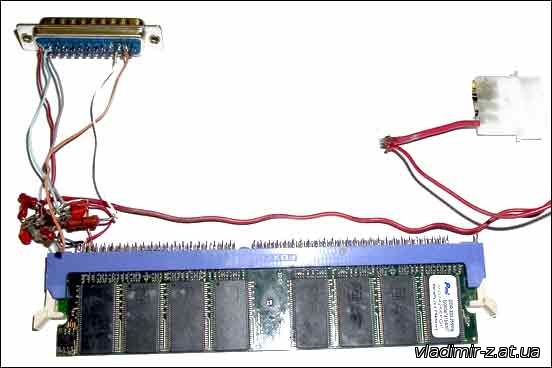

SPD и программатор Сейчас часто встречаются модули, которые имеют заниженные параметры. Также встречаются материнские платы, которые определяют тип памяти и жестко запрещают устанавливать частоту памяти большую записанной в SPD. Так, к примеру, при установке модуля DDR333 в материнские платы MSI K8N Neo, EPoX 8KDA3(+\J\I) и другие максимальная частота памяти ограничена 333 МГц (без разгона), хотя модуль возможно способен стабильно работать на более высоких частотах. Добиться частоты памяти равной частоте HT традиционными методами нет никакой возможности. Для этого приходилось использовать программу A64 Tweaker, которая может не всегда стабильно работать на разных платформах. Поэтому возникла потребность в программировании SPD. Превратив DDR333 в DDR400, мы легко решаем эту проблему, и разгон у нас ограничат только сами чипы памяти или процессор. Смысл использования SPD четко ясен для производителя, как модулей памяти, так и материнских плат, однако для конечного пользователя по большому счету интереса не представлял. Наличие схемы последовательного детектирования на модуле памяти избавляет производителей материнских плат от необходимости вносить оптимальные значения основных временных параметров в системный BIOS (как это делает, например, Intel, используя в своих материнских платах Phoenix BIOS), поскольку вся необходимая информация для нормальной настройки подсистемы и ее стабильного функционирования содержится в микросхеме SPD. Кроме этого, механизм SPD может настроить систему и гарантировать более-менее устойчивую работу при использовании в подсистеме памяти модулей разной организации, разного объема и имеющих разные значения одноименных параметров. Все, что нужно сделать контроллеру – это при инициализации системы считать записанные в SPD данные. Для программирования SPD был использован следующий "адаптер-программатор": Сборка данного устройства не должна вызвать каких-либо затруднений для людей видевших паяльник и транзистор. Транзисторы можно использовать любые типа n-p-n, в нашем случае это были KT315Б и BC817 в SMD корпусе. Вид программатора может быть таким (это тестовый прототип, только для того, чтобы убедится, что все работает):

Я использовал DDR DIMM разъем с материнской платы для большего удобства при прошивке большого количества модулей. Также преимущество данного подхода в сохранении гарантийного вида модулей памяти. Однако можно и напрямую подпаять провода к EEPROM на плате, не выпаивая ее. Все необходимые сигналы выведены на разъеме DDR DIMM. EEPROM установленная на плате модуля имеет выводы A0,A1,A2,WP(TEST) соединенные с землей (GND).

Ну а те же, кто считает такую конструкцию ненадежной и опасной может сделать плату, Например, как мою:

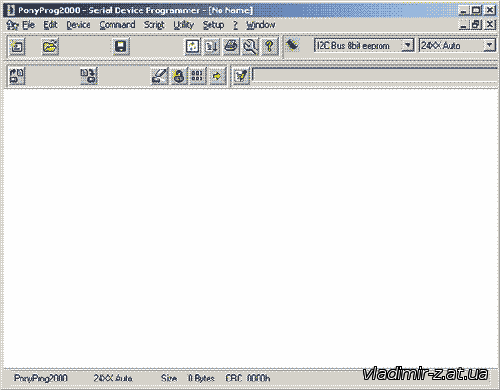

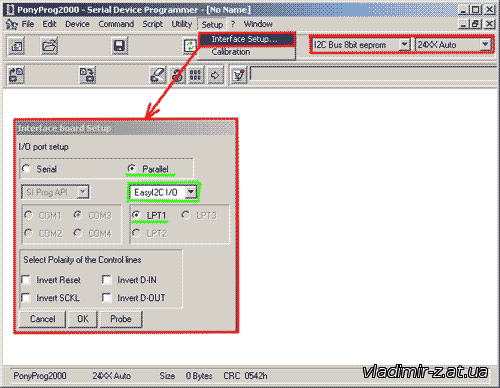

Размер платы не превышает размеров современного мобильного телефона. Это полная схема программатора с дополнительным стабилизатором на 5В. Если кого-то заинтересует информация по плате либо схеме, в конце статьи приведена контактная информация. В плате использовались SMD компоненты: транзисторы BC817, резисторы размера 1206, стабилизатор 5V, три светодиода (SDA, SCL и Power). Схема требует питания +9-30 V. Было применено питание +12V с БП ПК. Соединительные провода программатора к чипу следует делать минимально короткими, во избежание наводок и помех. Не спешите сразу припаивать чип к программатору, сначала включите его отдельно. Если у вас все спаяно верно и ничего не взорвалось, проверьте соединительный кабель и только затем, выключив схему, припаивайте чип или плату. Так же не стоит использовать большие паяльники мощностью более 25 Вт, иначе есть возможность сжечь детали. Для чтения или записи данных с чипа использовал freeware-программу PonyProg 2000. Процедура настройки и работы следующая: при первом запуске программы вы должны увидеть такое окно:

Первоначальная настройка заключается в следующем: необходимо выбрать тип прошиваемой памяти – I2C Bus 8bit EEPROM, а микросхему – 24XX Auto или 2402. Это делается при помощи выпадающих меню в верхней правой части. Затем в меню Setup > Interface Setup... нужно установить тип программатора, который используется. В нашем случае это EasyI2C I/O. Поскольку этот программатор имеет параллельный интерфейс, следует выбрать порт LPT1. В конечном виде все должно быть в точности как на скриншоте ниже:

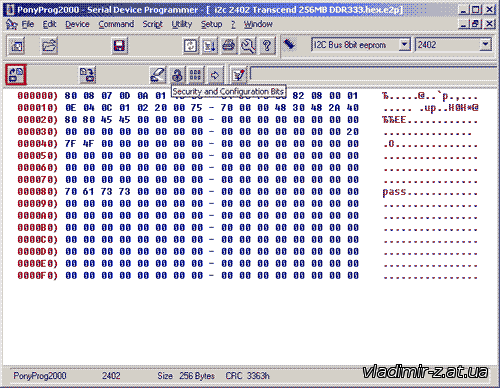

Теперь необходимо подключить программатор с подключенной микросхемой и считать ее. Для этого предназначена кнопка Read Device. После удачной процедуры чтения у вас должно быть на экране нечто похожее:

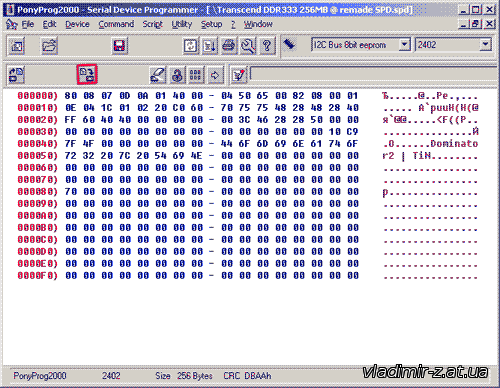

Если же у вас модуль не считался, проверьте правильность сборки, возможно, вы перепутали сигналы SCL и SDA. Можно записать считанные данные на диск из меню File. Настоятельно советую Вам это сделать, чтобы всегда можно было вернуться, если что-либо пойдет не так. Программа поддерживает редактирование считанных данных прямо в рабочем окне. Для этого вам нужно только активировать режим редактирования. Это делается в меню Edit, пункт Edit buffer enabled. После этого можете менять значения, точно так же, как и в любом HEX-редакторе. Сделав все, что вам было необходимо, нажимаете Write Device, показанную на скриншоте ниже и SPD EEPROM прошивается заданными данными. Данные после 128-го байта можно использовать на свое усмотрение, при работе ПК считывает только первые 128 байт. Можете записать туда свои пароли от Интернета или номер кредитной карты:-). После этого отключаете программатор и извлекаете модуль памяти.

Параметр контроллера памяти - DRAM Command Rate Сommand Rate устанавливает задержку поступления команд в память. Собственно, это понятие является синонимом задержки декодирования контроллером командно-адресной информации. За этим параметром скрывается выбор необходимого физического банка общего адресуемого пространства установленной системной памяти. Сама способность обработки команд с задержкой 1T зависит от таких факторов, как частота синхронизации шины памяти, количество микросхем на модуле памяти (чем больше микросхем, тем больше времени понадобится контроллеру, чтобы выбрать необходимую), качество используемого модуля, общее количество используемых модулей памяти в системе (прямо связано с количеством микросхем в составе одного модуля) и удаленность модуля от контроллера (протяженность сигнальных трасс от выводов контроллера до выводов микросхемы памяти с учетом количества переходов). Таким образом, если в системе с процессором на ядрах SledgeHammer, ClawHammer, NewCastle, Winchester используется два 2-банковых модуля, необходимо использовать 2Т, иначе сигналы доходят с ошибками. Позже будет проанализировано влияние этого параметра на скорость в целом. В процессорах на ядре Venice и последующих возможно использование параметра 1Т в системе с 4мя банками памяти без потери стабильности. В данной статье не будет приведено подробное описание остальных таймингов, т.к. цель исследования заключалась в выяснении максимально производительного режима для платформы Аthlon 64, а не изучении памяти. Если же потребуется детальная информация о таймингах обратитесь к статье "Настройка подсистемы памяти в BIOS SETUP". Для модификации SPD-данных вам понадобится нижеприведенная таблица адресов, и их значения. За "частоту модуля" отвечает байт 9. Если он равен 50 – это 5.0ns память, т.е. DDR400, 60 – 6.0ns – DDR333, 40 – 4.0ns – DDR500. Аналогичная ситуация и с другими таймингами.

Пример записи карты программирования SPD для небуферизированного 128MB-модуля 32Mx64, 184pin DDR SDRAM DIMM с адресацией 12/10/2, использующего микросхемы памяти организации 8Mx8 с периодом синхросигнала 7ns (-262) и 7.5ns (-265).

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Просмотров: 12553 | | | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Всего комментариев: 0 | |